Hablando de otra cosa, pero que es de lo mismo:

Si ya dominas la programación de los chips ARM, y el tema de las FPGA, ahora.... ¡une ambas cosas!

http://issuu.com/xcelljournal/docs/xcel ... doublePage

Es un SoC basado en ARM, pero que dentro del propio chip además de tener el ARM tienes una FPGA. Así puedes hacer lo que se llama codiseño, que consiste en que para resolver un problema, ciertas partes se codifican como programa que ejecuta el ARM, y otras partes se codifican como lógica pura.

Un ejemplo: pongamos que quieres hacer una aplicación en la que el ARM hace de encriptador/desencriptador en tiempo real de datos tales como video, sonido, o paquetes de red que llegan y salen por una ethernet. En software puedes hacer todo el tema de enrutamiento o encapsulamiento, y en hardware, añadir a tu SoC un módulo criptográfico que haga en pocos ciclos de reloj lo que en software tardarías cientos de ciclos.

En general: dado un algoritmo, detectar las partes de él que son más costosas en tiempo de ejecución y convertirlas a módulos hardware que hacen el mismo trabajo pero con circuitería lógica. Esos módulos aparecerán como periféricos al ARM, que los usará como si fueran periféricos ya existentes en el SoC.

Lo alucinante del asunto es que en algunos de estos "híbridos soft-hard" (no sé si éste es el caso), desde el ARM puedes reconfigurar en caliente lo que hay en la FPGA, y así puedes tener varios módulos hardware independientes entre sí, aunque cada uno de ellos se lleve todos los recursos lógicos de la FPGA. Cuando quieras usar uno de ellos, cargas la FPGA con la descripción correspondiente y la usas. Cuando quieres hacer otra cosa, pues cambias la configuración. Lo más virgueros permiten reconfigurar no toda la FPGA, sino bloques independientes, con lo que el proceso de reconfiguración es más rápido.

Papilio Pro ejecutando Arcade "Lady Bug"

- mcleod_ideafix

- Amiga 2500

- Mensajes: 5316

- Registrado: 06 Oct 2009, 04:12

- Sistema Favorito: Spectrum 16Kb/48Kb

- primer_sistema: Spectrum 16Kb/48Kb

- consola_favorita: Vectrex

- Primera consola: TV Games/Pong Clone

- Ubicación: Jerez de la Frontera

- Gracias dadas: 12 veces

- Gracias recibidas: 53 veces

- Contactar:

Re: Papilio Pro ejecutando Arcade "Lady Bug"

Recuerda: cada vez que se implementa un sistema clásico en FPGA, Dios mata a un purista

-

jepalza

Re: Papilio Pro ejecutando Arcade "Lady Bug"

Muuuuuuy interesante. Tengo que leerlo con mas calma. Precisamente estos días estoy programamdo el útimo ARM que me he comprado, y tengo lo del ARM calentito en la cabeza.

"yatoy" en casa: lo estoy mirando, y me gusta, pero ¿no hay forma de bajarse todo? es que ir hoja a hoja....

"yatoy" en casa: lo estoy mirando, y me gusta, pero ¿no hay forma de bajarse todo? es que ir hoja a hoja....

-

dssence

- ZX Spectrum 16

- Mensajes: 4

- Registrado: 21 Oct 2013, 11:57

- Sistema Favorito: Commodore Amiga

- primer_sistema: C64

- consola_favorita: (Otro)

- Primera consola: Nintendo GameBoy

Re: Papilio Pro ejecutando Arcade "Lady Bug"

Como estas!, la verdad que hace poco compre una de estas plaquitas es el micro que tiene es muy bueno. Queria preguntarte si me podrias dar una mano ya que compre el papilio pro pero sin los wings. Por ende el retrocade que estas emulando la placa que veo es para la salida VGA o tambien para el joystick? podrias ayudarme. Un abrazo!

- robcfg

- Amiga 2500

- Mensajes: 2138

- Registrado: 07 May 2009, 15:34

- Sistema Favorito: Amstrad CPC

- primer_sistema: Atari 800XL/600XL

- Ubicación: Estocolmo

- Gracias dadas: 852 veces

- Gracias recibidas: 168 veces

- Contactar:

Re: Papilio Pro ejecutando Arcade "Lady Bug"

Hola, seguramente si, te ayudará encantado, pero por favor, leete las normas del foro y presentate en la sección correspondiente.

Un saludo.

Un saludo.

-

jepalza

Re: Papilio Pro ejecutando Arcade "Lady Bug"

Aunque no es lo normal, y no me gusta que se "privatice" un tema, ya le estoy ayudando, por que me ha escrito varios correos esta mañana al correo particular.

Ahora me queda la duda: ¿sigo ayudándole por aquí, que todo el mundo se beneficie, o sigo por correos particulares?

Ahora me queda la duda: ¿sigo ayudándole por aquí, que todo el mundo se beneficie, o sigo por correos particulares?

- robcfg

- Amiga 2500

- Mensajes: 2138

- Registrado: 07 May 2009, 15:34

- Sistema Favorito: Amstrad CPC

- primer_sistema: Atari 800XL/600XL

- Ubicación: Estocolmo

- Gracias dadas: 852 veces

- Gracias recibidas: 168 veces

- Contactar:

Re: Papilio Pro ejecutando Arcade "Lady Bug"

Hombre, dependiendo de la cantidad de cosas, podriais poner un pequeño resumen cuando hayais acabado, para que sirva de referencia a los demas.

-

dssence

- ZX Spectrum 16

- Mensajes: 4

- Registrado: 21 Oct 2013, 11:57

- Sistema Favorito: Commodore Amiga

- primer_sistema: C64

- consola_favorita: (Otro)

- Primera consola: Nintendo GameBoy

Re: Papilio Pro ejecutando Arcade "Lady Bug"

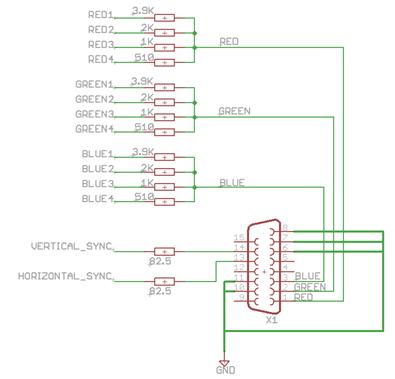

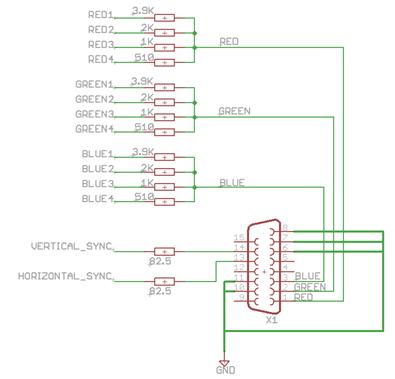

Bueno la verdad que no tuve tiempo para contar por aca como iba todo. Asi que quiero agradecer por la ayuda. Tengo unas dudas sobre los pinouts de papilio con respecto al esquematico . ASi que voy adjuntar un diagrama con mis comentarios.

El esquematico que me baje fue este de megawing

https://github.com/GadgetFactory/Papili ... gaWing.pdf

Aunque en la pagina por ejemplo para el wing de vga

No hay diodos ni capacitores, esa es mi duda quisiera saber la funcionalidad de esos diodos, y porque la linea de 3.3 volts va a cada uno de RED GREEN BLUE o me estoy equivocando

Es muy simple todo son simples conexiones y verificar que cada pinout vaya a su lugar, pero es mejor preguntar antes de mandarse alguna cagada y quemar algo.

El esquematico que me baje fue este de megawing

https://github.com/GadgetFactory/Papili ... gaWing.pdf

Aunque en la pagina por ejemplo para el wing de vga

No hay diodos ni capacitores, esa es mi duda quisiera saber la funcionalidad de esos diodos, y porque la linea de 3.3 volts va a cada uno de RED GREEN BLUE o me estoy equivocando

Es muy simple todo son simples conexiones y verificar que cada pinout vaya a su lugar, pero es mejor preguntar antes de mandarse alguna cagada y quemar algo.

-

jepalza

Re: Papilio Pro ejecutando Arcade "Lady Bug"

Perdona si no he respondido hasta ahora, he estado liado la semana.

Lo del pinout no te coincide, porque la placa en la que está conectado, no es la Papilio PRO, sino la OLS (Open Logic Sniffer) .

.

La foto no era para que vieras los pines, para eso, debes emplear el fichero UDF que te envié y el esquema oficial. Ademas, como ya te dije por correo, no estas obligado a esos pines, puedes adaptarlo a tu gusto según quieras o no ocupar una fila concreta. Es lo bueno de hacerlo uno mismo.

El esquema es la cosa mas simple del mundo, solo es un conjunto de resistencias (3x4) para dar profundidad a cada color. Nada mas. Todo lo demas del esquema sobra en un principio. Si no funciona con tu TV, entonces debes probar las resistencias atenuadoras de H y V y quizas la protección de los diodos, que según que TV quizas lo necesite.

Y por cierto, las resitencias no van a 3.3v., lo ves mal, can "al aire", por encima del circuito, ni lleva diodos. Mi TV no los necesita.

Y mas cosas, lo del CLK y DAT, si entiendes algo de electrónica, que me da que no, son las señales del PS2 de los PC (donde se conectan el teclado y ratón PS/2) que en mi placa los he añadido a mi gusto tambien. Por eso te digo, que lo de la foto es solo orientativo. Lo hice a mi gusto. Tú no deberías hacer lo mismo que yo, deberías buscar la mejor solución para ti.

Veo que quieres guiarte por la foto, y eso es un error: olvídate de la foto, como ya te dije, solo es para que veas lo que yo he hecho. Usa los esquemas oficiales de "solo resistencias", y listo. Eliges los pines que mas te gusten, y los cambias en el fichero UCF. Si ademas quieres PS2 y/o SD (lector de tarjetas), tienes que añadir mas lineas a tu placa, y lo mismo al fichero de configuración, y por supuesto, añadir el módulo al programa.

Y no me pidas un esquema de esa placa, por que no lo tengo. Trabajo "a ojo", sin esquemas, voy soldando y sale lo que sale. ¿que funciona? Aleluya, ¿que no funciona? a repasar hasta que lo haga. A la vieja usanza.

Lo del pinout no te coincide, porque la placa en la que está conectado, no es la Papilio PRO, sino la OLS (Open Logic Sniffer)

La foto no era para que vieras los pines, para eso, debes emplear el fichero UDF que te envié y el esquema oficial. Ademas, como ya te dije por correo, no estas obligado a esos pines, puedes adaptarlo a tu gusto según quieras o no ocupar una fila concreta. Es lo bueno de hacerlo uno mismo.

El esquema es la cosa mas simple del mundo, solo es un conjunto de resistencias (3x4) para dar profundidad a cada color. Nada mas. Todo lo demas del esquema sobra en un principio. Si no funciona con tu TV, entonces debes probar las resistencias atenuadoras de H y V y quizas la protección de los diodos, que según que TV quizas lo necesite.

Y por cierto, las resitencias no van a 3.3v., lo ves mal, can "al aire", por encima del circuito, ni lleva diodos. Mi TV no los necesita.

Y mas cosas, lo del CLK y DAT, si entiendes algo de electrónica, que me da que no, son las señales del PS2 de los PC (donde se conectan el teclado y ratón PS/2) que en mi placa los he añadido a mi gusto tambien. Por eso te digo, que lo de la foto es solo orientativo. Lo hice a mi gusto. Tú no deberías hacer lo mismo que yo, deberías buscar la mejor solución para ti.

Veo que quieres guiarte por la foto, y eso es un error: olvídate de la foto, como ya te dije, solo es para que veas lo que yo he hecho. Usa los esquemas oficiales de "solo resistencias", y listo. Eliges los pines que mas te gusten, y los cambias en el fichero UCF. Si ademas quieres PS2 y/o SD (lector de tarjetas), tienes que añadir mas lineas a tu placa, y lo mismo al fichero de configuración, y por supuesto, añadir el módulo al programa.

Y no me pidas un esquema de esa placa, por que no lo tengo. Trabajo "a ojo", sin esquemas, voy soldando y sale lo que sale. ¿que funciona? Aleluya, ¿que no funciona? a repasar hasta que lo haga. A la vieja usanza.

-

dssence

- ZX Spectrum 16

- Mensajes: 4

- Registrado: 21 Oct 2013, 11:57

- Sistema Favorito: Commodore Amiga

- primer_sistema: C64

- consola_favorita: (Otro)

- Primera consola: Nintendo GameBoy

Re: Papilio Pro ejecutando Arcade "Lady Bug"

Como estas gracias por responder , si entiendo de electronica lo que pasaba que no encontraba la logica en la foto porque pensaba que estabas conectando en la papilio pro todo y estabas solamente haciendo el circuito para la salida VGA por eso no entendia los demas pines y tampoco entendia que no coincidian.

El archivo ese que me decis , te pregunto porque todavia no arranque con la papilio. Me baje de Xilinx la ISE design suite. Dame un pantallazo asi general.

- El archivo que me decis UCF es en donde definis los pines y la logica del FPGA ?. En caso que yo quiera usar los esquematicos del megawing que te pase me imagino que estan asignados dentro del esquema por default de la placa, entonces necesitaria usar los pines asignados por defecto no ?

- Todavia no lo conecte el papilio pro cuando lo haga ya viene la FPGA cargada con algun programa por defecto que hace blink al led ? . Esta con el UCF por defecto?

- Para programar el FGPA necesito el Loader de la pagina , el ISE design suite se usa solamente para sintetizar?

Abrazo ! me baje este libro de hamster IntroToSpartanFPGABook-master.zip que tiene codigo adentro pero no es para el LX9

El archivo ese que me decis , te pregunto porque todavia no arranque con la papilio. Me baje de Xilinx la ISE design suite. Dame un pantallazo asi general.

- El archivo que me decis UCF es en donde definis los pines y la logica del FPGA ?. En caso que yo quiera usar los esquematicos del megawing que te pase me imagino que estan asignados dentro del esquema por default de la placa, entonces necesitaria usar los pines asignados por defecto no ?

- Todavia no lo conecte el papilio pro cuando lo haga ya viene la FPGA cargada con algun programa por defecto que hace blink al led ? . Esta con el UCF por defecto?

- Para programar el FGPA necesito el Loader de la pagina , el ISE design suite se usa solamente para sintetizar?

Abrazo ! me baje este libro de hamster IntroToSpartanFPGABook-master.zip que tiene codigo adentro pero no es para el LX9

-

jepalza

Re: Papilio Pro ejecutando Arcade "Lady Bug"

El UCF solo indica los pines de entrada/salida del Xilinx y la velocidad del reloj. El resto, lo "programas" por decirlo de un modo (lo sintetizas). En el UCF indicas que llevas conectado a cada pin.

Este es el original, de la página oficial:

Si lo miras detenidamene, verás la asignacion de cada pin. Muchos ya llevan asignación por defecto, y no se pueden cambiar, como los del JTAG o los de la SDRAM. Los que quedan libres, lo empleas a tu gusto. Lo puedes habilitar como entrad, como salida, lentos, rápidos... (eso, queda fuera de lo que hablamos aquí, es cosa de "estudiar" Xilinx)

El fichero compilado (normalmente extensión BIT), lleva los módulos que tu has acoplado (por ejemplo, una CPU, la SDRAM, la salida a VGA), con los pines que tu has elegido (o con los fijos, como los de la SDRAM), y relacionados con el UCF. Realmente, tú solo tocas el UCF a tu gusto, y esos pines, los llevas a los módulos que vas a sintetizar.

Con el fichero BIT, te vas al "loader" oficial (creo que se llama "papilio loader v2.1", y el resto es automático, solo eliges el BIT, y el programa busca el puerto COM al que lo tengas, y lo actualiza.

El programa de XILINX (el ISE) solo lo usas para "programar", pero no paa subir el código al Papilio. Si viene con la demo de "led parpadeante", no lo recuerdo, por que a mi me duró segundos virgen. Nada mas llegar, ya le metí unas demos para probarlo.

En el programa ISE es donde debes definir los valores del Papilio, como el chip que lleva, el tipo de encapsulado, etc. Esos valores, ahora no los recuerdo, y el Xilinx (como ya te dije por correo), no lo empleo desde marzo por lo menos, y no lo tengo instalado. Lo quité por que ocupa demasiados gigas y excesivos ficheros, y por que ahora no estoy haciendo nada con el Xilinx, sino con el ARM. Pero son valores, que los tienes en la página del fabricante.

Para esas cosas, necesitas manuales XILINX, y eso queda lejos del alcance de lo que pretendemos aquí.

No pretendo ponerme a dar un cursillo de programación y manejo del Papilio y el Xilix (Verilog), que eso lleva muuucho tiempo, y ya existen manuales (como se suele decir, mi tiempo es oro, como para pasarme horas escribiendo un manual, del cual ya hay docenas por la red)

-- Actualizado 24 Oct 2013, 22:28 --

El UCF no está o deja de estar: lo añades en cada trabajo adaptado a los módulos que estas empleando en ese momento. Si no empleas los pines, no se habilitan. En la demo del "led parpadeante", estoy convencido, que el 100% de los pines libres, siguen libres, no hacen nada, conectes lo que conectes. Si programas algo que emplee 5 pines para el RGB+HV, y por error olvidas uno de ellos en el enlace de los módulos, cuando pasas el BIT al papilio, ese pin olvidado, queda vacío, sin función.

Se me olvida comentar (y creo que es bastante obvio), que para subir al papilio una demo o un juego hecho por otro, no necesitas para nada el ISE, solo el LOADER. EL ISE es solo para jugar modificando las cosas o creando tus propio juegos.

Este es el original, de la página oficial:

Código: Seleccionar todo

# UCF file for the Papilio Pro board

# Generated by pin_converter, written by Kevin Lindsey

# https://github.com/thelonious/papilio_pins/tree/development/pin_converter

# Main board wing pin [] to FPGA pin Pxx map

# -------C------- -------B------- -------A-------

# [GND] [C00] P114 [GND] [B00] P99 P100 [A15]

# [2V5] [C01] P115 [2V5] [B01] P97 P98 [A14]

# [3V3] [C02] P116 [3V3] [B02] P92 P93 [A13]

# [5V0] [C03] P117 [5V0] [B03] P87 P88 [A12]

# [C04] P118 [B04] P84 P85 [A11] [5V0]

# [C05] P119 [B05] P82 P83 [A10] [3V3]

# [C06] P120 [B06] P80 P81 [A09] [2V5]

# [C07] P121 [B07] P78 P79 [A08] [GND]

# [GND] [C08] P123 [GND] [B08] P74 P75 [A07]

# [2V5] [C09] P124 [2V5] [B09] P95 P67 [A06]

# [3V3] [C10] P126 [3V3] [B10] P62 P66 [A05]

# [5V0] [C11] P127 [5V0] [B11] P59 P61 [A04]

# [C12] P131 [B12] P57 P58 [A03] [5V0]

# [C13] P132 [B13] P55 P56 [A02] [3V3]

# [C14] P133 [B14] P50 P51 [A01] [2V5]

# [C15] P134 [B15] P47 P48 [A00] [GND]

## Prohibit the automatic placement of pins that are connected to VCC or GND for configuration.

CONFIG PROHIBIT=P144;

CONFIG PROHIBIT=P69;

CONFIG PROHIBIT=P60;

NET CLK LOC="P94" | IOSTANDARD=LVTTL | PERIOD=31.25ns; # CLK

NET RX LOC="P101" | IOSTANDARD=LVTTL | DRIVE=8 | SLEW=FAST; # RX

NET TX LOC="P105" | IOSTANDARD=LVTTL | DRIVE=8 | SLEW=FAST | PULLUP; # TX

NET A(0) LOC="P48" | IOSTANDARD=LVTTL; # A0

NET A(1) LOC="P51" | IOSTANDARD=LVTTL; # A1

NET A(2) LOC="P56" | IOSTANDARD=LVTTL; # A2

NET A(3) LOC="P58" | IOSTANDARD=LVTTL; # A3

NET A(4) LOC="P61" | IOSTANDARD=LVTTL; # A4

NET A(5) LOC="P66" | IOSTANDARD=LVTTL; # A5

NET A(6) LOC="P67" | IOSTANDARD=LVTTL; # A6

NET A(7) LOC="P75" | IOSTANDARD=LVTTL; # A7

NET A(8) LOC="P79" | IOSTANDARD=LVTTL; # A8

NET A(9) LOC="P81" | IOSTANDARD=LVTTL; # A9

NET A(10) LOC="P83" | IOSTANDARD=LVTTL; # A10

NET A(11) LOC="P85" | IOSTANDARD=LVTTL; # A11

NET A(12) LOC="P88" | IOSTANDARD=LVTTL; # A12

NET A(13) LOC="P93" | IOSTANDARD=LVTTL; # A13

NET A(14) LOC="P98" | IOSTANDARD=LVTTL; # A14

NET A(15) LOC="P100" | IOSTANDARD=LVTTL; # A15

NET B(0) LOC="P99" | IOSTANDARD=LVTTL; # B0

NET B(1) LOC="P97" | IOSTANDARD=LVTTL; # B1

NET B(2) LOC="P92" | IOSTANDARD=LVTTL; # B2

NET B(3) LOC="P87" | IOSTANDARD=LVTTL; # B3

NET B(4) LOC="P84" | IOSTANDARD=LVTTL; # B4

NET B(5) LOC="P82" | IOSTANDARD=LVTTL; # B5

NET B(6) LOC="P80" | IOSTANDARD=LVTTL; # B6

NET B(7) LOC="P78" | IOSTANDARD=LVTTL; # B7

NET B(8) LOC="P74" | IOSTANDARD=LVTTL; # B8

NET B(9) LOC="P95" | IOSTANDARD=LVTTL; # B9

NET B(10) LOC="P62" | IOSTANDARD=LVTTL; # B10

NET B(11) LOC="P59" | IOSTANDARD=LVTTL; # B11

NET B(12) LOC="P57" | IOSTANDARD=LVTTL; # B12

NET B(13) LOC="P55" | IOSTANDARD=LVTTL; # B13

NET B(14) LOC="P50" | IOSTANDARD=LVTTL; # B14

NET B(15) LOC="P47" | IOSTANDARD=LVTTL; # B15

NET C(0) LOC="P114" | IOSTANDARD=LVTTL; # C0

NET C(1) LOC="P115" | IOSTANDARD=LVTTL; # C1

NET C(2) LOC="P116" | IOSTANDARD=LVTTL; # C2

NET C(3) LOC="P117" | IOSTANDARD=LVTTL; # C3

NET C(4) LOC="P118" | IOSTANDARD=LVTTL; # C4

NET C(5) LOC="P119" | IOSTANDARD=LVTTL; # C5

NET C(6) LOC="P120" | IOSTANDARD=LVTTL; # C6

NET C(7) LOC="P121" | IOSTANDARD=LVTTL; # C7

NET C(8) LOC="P123" | IOSTANDARD=LVTTL; # C8

NET C(9) LOC="P124" | IOSTANDARD=LVTTL; # C9

NET C(10) LOC="P126" | IOSTANDARD=LVTTL; # C10

NET C(11) LOC="P127" | IOSTANDARD=LVTTL; # C11

NET C(12) LOC="P131" | IOSTANDARD=LVTTL; # C12

NET C(13) LOC="P132" | IOSTANDARD=LVTTL; # C13

NET C(14) LOC="P133" | IOSTANDARD=LVTTL; # C14

NET C(15) LOC="P134" | IOSTANDARD=LVTTL; # C15

NET SDRAM_ADDR(0) LOC="P140" | IOSTANDARD=LVTTL; # SDRAM_ADDR0

NET SDRAM_ADDR(1) LOC="P139" | IOSTANDARD=LVTTL; # SDRAM_ADDR1

NET SDRAM_ADDR(2) LOC="P138" | IOSTANDARD=LVTTL; # SDRAM_ADDR2

NET SDRAM_ADDR(3) LOC="P137" | IOSTANDARD=LVTTL; # SDRAM_ADDR3

NET SDRAM_ADDR(4) LOC="P46" | IOSTANDARD=LVTTL; # SDRAM_ADDR4

NET SDRAM_ADDR(5) LOC="P45" | IOSTANDARD=LVTTL; # SDRAM_ADDR5

NET SDRAM_ADDR(6) LOC="P44" | IOSTANDARD=LVTTL; # SDRAM_ADDR6

NET SDRAM_ADDR(7) LOC="P43" | IOSTANDARD=LVTTL; # SDRAM_ADDR7

NET SDRAM_ADDR(8) LOC="P41" | IOSTANDARD=LVTTL; # SDRAM_ADDR8

NET SDRAM_ADDR(9) LOC="P40" | IOSTANDARD=LVTTL; # SDRAM_ADDR9

NET SDRAM_ADDR(10) LOC="P141" | IOSTANDARD=LVTTL; # SDRAM_ADDR10

NET SDRAM_ADDR(11) LOC="P35" | IOSTANDARD=LVTTL; # SDRAM_ADDR11

NET SDRAM_ADDR(12) LOC="P34" | IOSTANDARD=LVTTL; # SDRAM_ADDR12

NET SDRAM_DATA(0) LOC="P9" | IOSTANDARD=LVTTL; # SDRAM_DATA0

NET SDRAM_DATA(1) LOC="P10" | IOSTANDARD=LVTTL; # SDRAM_DATA1

NET SDRAM_DATA(2) LOC="P11" | IOSTANDARD=LVTTL; # SDRAM_DATA2

NET SDRAM_DATA(3) LOC="P12" | IOSTANDARD=LVTTL; # SDRAM_DATA3

NET SDRAM_DATA(4) LOC="P14" | IOSTANDARD=LVTTL; # SDRAM_DATA4

NET SDRAM_DATA(5) LOC="P15" | IOSTANDARD=LVTTL; # SDRAM_DATA5

NET SDRAM_DATA(6) LOC="P16" | IOSTANDARD=LVTTL; # SDRAM_DATA6

NET SDRAM_DATA(7) LOC="P8" | IOSTANDARD=LVTTL; # SDRAM_DATA7

NET SDRAM_DATA(8) LOC="P21" | IOSTANDARD=LVTTL; # SDRAM_DATA8

NET SDRAM_DATA(9) LOC="P22" | IOSTANDARD=LVTTL; # SDRAM_DATA9

NET SDRAM_DATA(10) LOC="P23" | IOSTANDARD=LVTTL; # SDRAM_DATA10

NET SDRAM_DATA(11) LOC="P24" | IOSTANDARD=LVTTL; # SDRAM_DATA11

NET SDRAM_DATA(12) LOC="P26" | IOSTANDARD=LVTTL; # SDRAM_DATA12

NET SDRAM_DATA(13) LOC="P27" | IOSTANDARD=LVTTL; # SDRAM_DATA13

NET SDRAM_DATA(14) LOC="P29" | IOSTANDARD=LVTTL; # SDRAM_DATA14

NET SDRAM_DATA(15) LOC="P30" | IOSTANDARD=LVTTL; # SDRAM_DATA15

NET SDRAM_DQML LOC="P7" | IOSTANDARD=LVTTL; # SDRAM_DQML

NET SDRAM_DQMH LOC="P17" | IOSTANDARD=LVTTL; # SDRAM_DQMH

NET SDRAM_BA(0) LOC="P143" | IOSTANDARD=LVTTL; # SDRAM_BA0

NET SDRAM_BA(1) LOC="P142" | IOSTANDARD=LVTTL; # SDRAM_BA1

NET SDRAM_nWE LOC="P6" | IOSTANDARD=LVTTL; # SDRAM_nWE

NET SDRAM_nCAS LOC="P5" | IOSTANDARD=LVTTL; # SDRAM_nCAS

NET SDRAM_nRAS LOC="P2" | IOSTANDARD=LVTTL; # SDRAM_nRAS

NET SDRAM_CS LOC="P1" | IOSTANDARD=LVTTL; # SDRAM_CS

NET SDRAM_CLK LOC="P32" | IOSTANDARD=LVTTL; # SDRAM_CLK

NET SDRAM_CKE LOC="P33" | IOSTANDARD=LVTTL; # SDRAM_CKE

NET LED1 LOC="P112" | IOSTANDARD=LVTTL | DRIVE=8 | SLEW=SLOW; # LED1

NET JTAG_TMS LOC="P107" | IOSTANDARD=LVTTL | DRIVE=8 | SLEW=FAST; # JTAG_TMS

NET JTAG_TCK LOC="P109" | IOSTANDARD=LVTTL | DRIVE=8 | SLEW=FAST; # JTAG_TCK

NET JTAG_TDI LOC="P110" | IOSTANDARD=LVTTL | DRIVE=8 | SLEW=FAST; # JTAG_TDI

NET JTAG_TDO LOC="P106" | IOSTANDARD=LVTTL | DRIVE=8 | SLEW=FAST; # JTAG_TDO

NET FLASH_CS LOC="P38" | IOSTANDARD=LVTTL | DRIVE=8 | SLEW=FAST; # FLASH_CS

NET FLASH_CK LOC="P70" | IOSTANDARD=LVTTL | DRIVE=8 | SLEW=FAST; # FLASH_CK

NET FLASH_SI LOC="P64" | IOSTANDARD=LVTTL | DRIVE=8 | SLEW=FAST; # FLASH_SI

NET FLASH_SO LOC="P65" | IOSTANDARD=LVTTL | DRIVE=8 | SLEW=FAST | PULLUP; # FLASH_SO

Si lo miras detenidamene, verás la asignacion de cada pin. Muchos ya llevan asignación por defecto, y no se pueden cambiar, como los del JTAG o los de la SDRAM. Los que quedan libres, lo empleas a tu gusto. Lo puedes habilitar como entrad, como salida, lentos, rápidos... (eso, queda fuera de lo que hablamos aquí, es cosa de "estudiar" Xilinx)

El fichero compilado (normalmente extensión BIT), lleva los módulos que tu has acoplado (por ejemplo, una CPU, la SDRAM, la salida a VGA), con los pines que tu has elegido (o con los fijos, como los de la SDRAM), y relacionados con el UCF. Realmente, tú solo tocas el UCF a tu gusto, y esos pines, los llevas a los módulos que vas a sintetizar.

Con el fichero BIT, te vas al "loader" oficial (creo que se llama "papilio loader v2.1", y el resto es automático, solo eliges el BIT, y el programa busca el puerto COM al que lo tengas, y lo actualiza.

El programa de XILINX (el ISE) solo lo usas para "programar", pero no paa subir el código al Papilio. Si viene con la demo de "led parpadeante", no lo recuerdo, por que a mi me duró segundos virgen. Nada mas llegar, ya le metí unas demos para probarlo.

En el programa ISE es donde debes definir los valores del Papilio, como el chip que lleva, el tipo de encapsulado, etc. Esos valores, ahora no los recuerdo, y el Xilinx (como ya te dije por correo), no lo empleo desde marzo por lo menos, y no lo tengo instalado. Lo quité por que ocupa demasiados gigas y excesivos ficheros, y por que ahora no estoy haciendo nada con el Xilinx, sino con el ARM. Pero son valores, que los tienes en la página del fabricante.

Para esas cosas, necesitas manuales XILINX, y eso queda lejos del alcance de lo que pretendemos aquí.

No pretendo ponerme a dar un cursillo de programación y manejo del Papilio y el Xilix (Verilog), que eso lleva muuucho tiempo, y ya existen manuales (como se suele decir, mi tiempo es oro, como para pasarme horas escribiendo un manual, del cual ya hay docenas por la red)

-- Actualizado 24 Oct 2013, 22:28 --

dssence escribió: Esta con el UCF por defecto?

El UCF no está o deja de estar: lo añades en cada trabajo adaptado a los módulos que estas empleando en ese momento. Si no empleas los pines, no se habilitan. En la demo del "led parpadeante", estoy convencido, que el 100% de los pines libres, siguen libres, no hacen nada, conectes lo que conectes. Si programas algo que emplee 5 pines para el RGB+HV, y por error olvidas uno de ellos en el enlace de los módulos, cuando pasas el BIT al papilio, ese pin olvidado, queda vacío, sin función.

Se me olvida comentar (y creo que es bastante obvio), que para subir al papilio una demo o un juego hecho por otro, no necesitas para nada el ISE, solo el LOADER. EL ISE es solo para jugar modificando las cosas o creando tus propio juegos.

Volver a “Máquinas recreativas”

¿Quién está conectado?

Usuarios navegando por este Foro: No hay usuarios registrados visitando el Foro y 2 invitados