[quote="antoniovillena"]Estoy haciendo un recuento de pines para ver lo que necesitamos:

¿Por qué usar dos buses SPI si puedes comandar dos esclavos SPI con el mismo bus? Las señales MISO, MOSI y SCLK serían comunes a SD y Flash, y es la señal SS la que es diferente para cada esclavo. Con esto pasarías de 8 a 5 pines.

¿Cómo se detallan estos 29 pines? Entiendo que 8 son el bus de datos, y 1 para la señal de escritura. La RAM puede estar seleccionada permanentemente (CS=0) y permanentemente habilitada (OE=0) por lo que quedan 20 pines para el bus de direcciones, que da 1MB. ¿Es así?

¿De dónde sale el 45? Haciendo la cuenta...

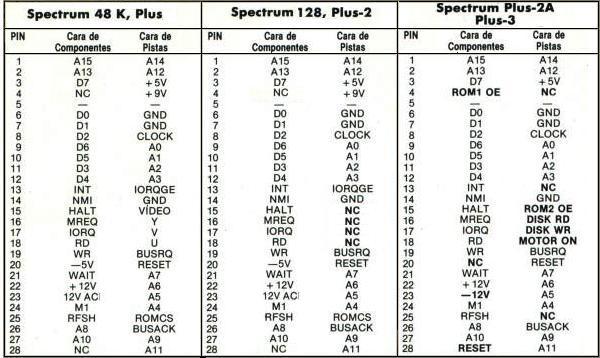

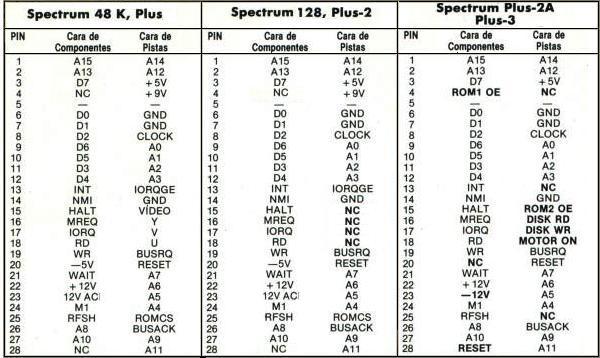

- Bus de direcciones: 16

- Bus de datos: 8

- Control de memoria y E/S: MREQ, IORQ, RD, WR: 4

- Control del bus: M1, HALT, WAIT, BUSRQ, BUSAK: 5

- Interrupciones y reset: NMI, INT, RESET: 3

- Reloj: 1

- Control de la ULA: IORQGE: 1

- Refresco e inhabilitación ROM. RFSH y ROMCS: 2

Me salen 40 pines de la FPGA, no 45.

Con el ahorro de pines en el SPI, me sale un total de 90 pines a usar en la FPGA. Incluso podemos tirarnos el pegote y añadir una versión negada de la señal de sincronismos (o negarla fuera) y rutarla por la salida Y del slot de expansión, para que la interface SPECTRA esté contenta

(o algo más útil: una entrada de joystick, que serían 5 pines más)